- Los rendimientos perdidos de los estoccastics están gastando miles de millones de ardores en los nodos

- Los métodos de control de procesos actuales no son suficientes para resolver fallas estocusas de alto volumen

- Describe las soluciones de diseño y medición para cerrar la nueva brecha de estocusos blancos

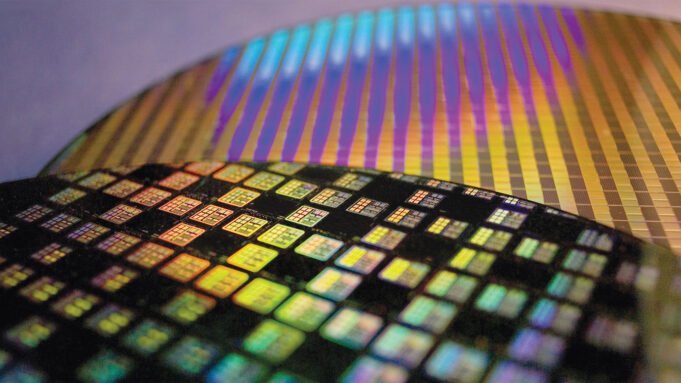

Un nuevo documento técnico ha afirmado que el semiconductor ha escuchado algo fuera del campo: perder unos mil millones de dólares debido a la variabilidad estocusta.

Esta forma de variedad de patrones aleatorios ahora se considera la mayor barrera para lograr altos rendimientos en los nodos de proceso más avanzados.

El documento aportado por Fractilia Austin, con sede en Texas, cuyo CTO, Chris Mac señaló, “la variabilidad estocástica está contribuyendo al lanzamiento de miles de millones de dólares en la introducción de la tecnología de procesos avanzados en la producción de alto volumen”.

Afectar el rendimiento, el rendimiento y la fiabilidad

Mac explicó además que las técnicas actuales de control del proceso no pudieron resolver estos efectos aleatorios.

Mac dijo: “Los estoccastics deben detener el intervalo que requiere un método completamente diferente que los fabricantes de dispositivos deben ser validados y aceptados”, dijo Mac.

La fractilia define esta “brecha estocástica” que puede ser patrocinada en el estudio y la clave para la clave de los rendimientos aceptables puede producirse de manera confiable como la diferencia entre la masa.

El enfoque de este intervalo es un aleatorio de la física de los materiales, moléculas y fuentes de luz utilizadas en la producción de chips.

Aunque estos efectos alguna vez fueron insignificantes, ahora toman la parte creciente del presupuesto de errores de producción.

“Hemos visto pequeñas características como 12 nanómetros en investigación y desarrollo”, dijo Mac, dijo Mac. “Pero cuando intentan transferirlo a la producción, la falla estocástica afecta su capacidad para lograr rendimientos, rendimiento y confiabilidad aceptables”.

El problema ha aumentado junto con el aumento de EUV y la litografía de alta nau. Estos progresos han permitido a los fabricantes de chips intentar probar características más pequeñas, pero las debilitan por defectos estocusos.

A diferencia de las variables convencionales, tales controles estrictos no pueden ser eliminados, debe administrarse con técnicas de diseño y medición basadas en viabilidad.

“La brecha entre la estocusia es un problema industrial”, dijo Mac. “Este problema puede ser mínimo y controlado, pero comienza con toda la tecnología de medición de estocusos correcta”.

Whitepaper, que puedes descargar AquíEl análisis del problema incluye un diseño consciente de los estocásticos, la innovación de los materiales y la actualización del proceso de actualización como un camino a seguir.